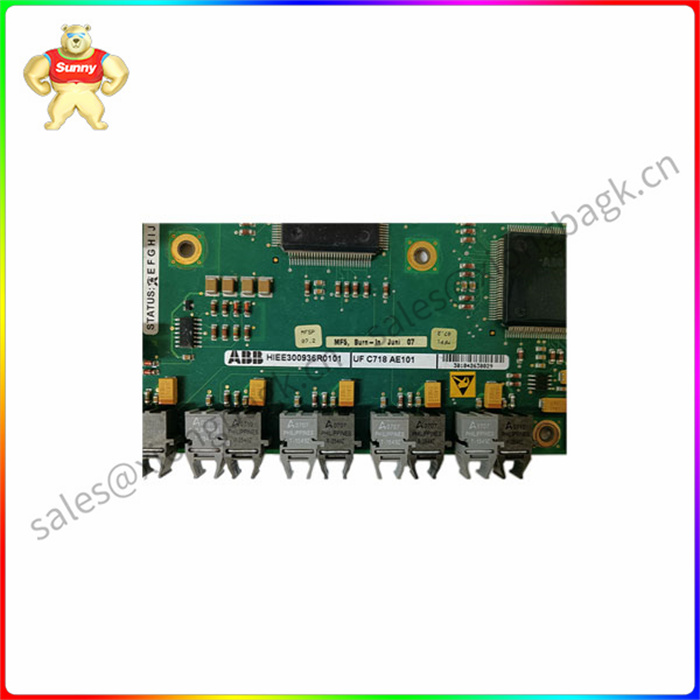

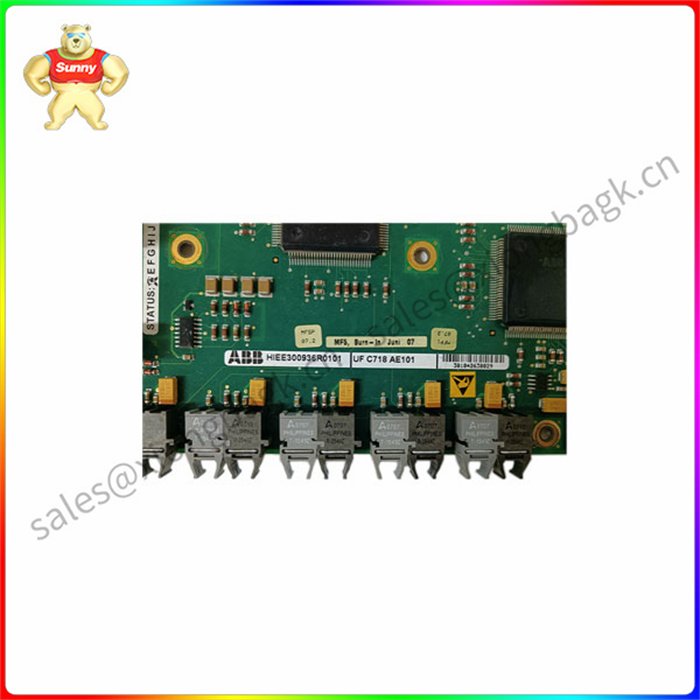

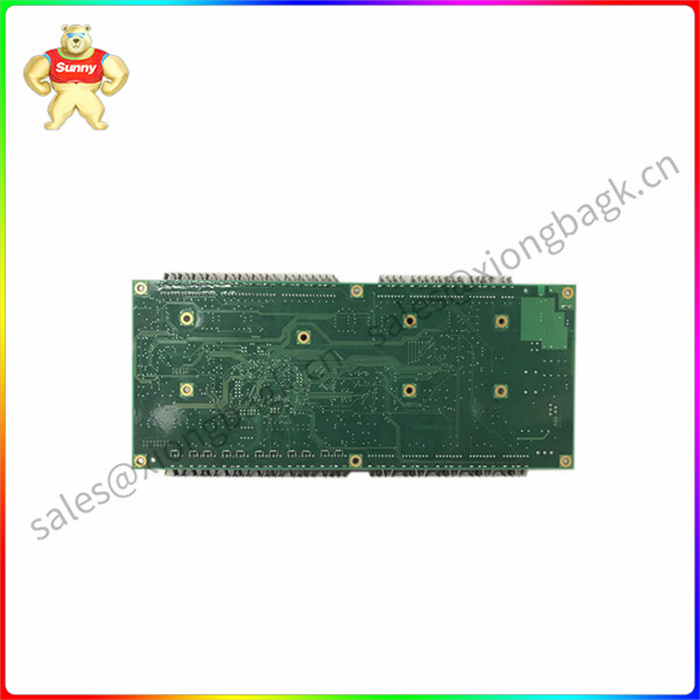

UFC718AE101 ABB 使用通道通过UBS连接器传输数据

1 相位累加器

对于利用FPGA设计DDS信号源,相位累加器是决定DDS电路性能的一个关键部分。相位累加器是由N位累加器和N位寄存器级联构成,每来一个时钟脉冲,相位寄存器采样上个时钟周期内相位累加器的值与频率控制字K之和,并作为相位累加器在这一时钟周期的输出。由式(2)可知,相位累加器的位数N越大,得到的频率分辨率越小,但在较高的工作频率下,会产生较大的延时不能满足速度的要求。在时序电路中,通常采用流水线技术来提高速度,代价是增加寄存器的数量,多占了FPGA的资料。综合考虑,采用32位累加器,四级流水线结构。

2.1.2 相位-幅度变换器

相位-幅度变换器是由ROM构成,它把相位累加器的输出的数字相位信息变换成正弦波值。在FPGA中,ROM一般是由EAB来实现,并且ROM表的尺寸与地址位数或数据位数成指数增加的关系,因此相位-幅度转换器的设计是影响DDS性能的另一个关键,在满足信号设计指标要求的前提下,主要在于减少资源开销。考虑到本设计只需要输出正弦信号,正弦波信号关于点(π,0)奇对称,只需存储1/2周期的波形数据,又根据在左半周期内,波形关于直线x=π/2成偶对称,因此只需要存储1/4周期的正弦函数值,就可以通过适当的变换得到整个正弦码表,这样可以节约3/4的资源。

2. 2 低通滤波模块

DDS有一个明显的缺点,即输出频率越接近Nyquist带宽的高端,采样点数越少,其输出的杂散干扰就越大。输出波形具有大量的谐波分量和系统时钟干扰。为得到所需频段内的信号,需要在DDS输出端加一滤波器来实现,而低通滤波器能较好地滤除杂波,平滑信号,所以低通滤波器的设计尤为重要,滤波特性的优劣对输出信号的性能起重要的影响。

为取得较好的滤波效果,滤波器采用了由四选一模拟开关和精密运算放大器分段滤波的方式:采用巴特沃斯有源低通滤波器,该滤波器通带内幅度很平坦,滤波电路为二阶巴特沃斯低通滤波电路,滤波器频段参数的选择由FPGA输出的控制信号nINH,S0,S1控制模拟开关的选通实现。

UFC718AE101 ABB 使用通道通过UBS连接器传输数据

1 Phase accumulator

For the design of DDS signal source using FPGA, the phase accumulator is a key part to determine the performance of DDS circuit. The phase accumulator is composed of an n-bit accumulator and an N-bit register cascade. For each clock pulse, the phase register samples the sum of the value of the phase accumulator and the frequency control word K in the previous clock cycle, and acts as the output of the phase accumulator in this clock cycle. As can be seen from formula (2), the larger the bit N of the phase accumulator, the smaller the frequency resolution, but at a higher operating frequency, a larger delay will be generated which cannot meet the requirements of speed. In sequential circuits, pipelining technology is usually used to improve speed, at the cost of increasing the number of registers, which accounts for more data in FPGA. Overall consideration, the use of 32-bit accumulator, four-stage pipeline structure.

2.1.2 Phase-amplitude converter

The phase-amplitude converter is composed of ROM, which converts the digital phase information of the output of the phase accumulator into a sine wave value. In FPGA, ROM is generally implemented by EAB, and the size of ROM table increases exponentially with the address bits or data bits, so the design of phase-amplitude converter is another key to affect the performance of DDS, which is mainly to reduce resource overhead under the premise of meeting the requirements of signal design indicators. Considering that this design only needs to output sinusoidal signal, sine wave signal about the point (π, 0) odd symmetry, only need to store 1/2 cycle waveform data, and according to the left half cycle, waveform about the line x=π / 2 even symmetry, so only need to store 1/4 cycle sine function value, you can get the whole sine code table through appropriate transformation. This saves three quarters of the resources.

2. 2 Low-Pass filtering module

DDS has an obvious disadvantage, that the closer the output frequency is to the high end of the Nyquist bandwidth, the fewer the sampling points, and the greater the stray interference of its output. The output waveform has a lot of harmonic components and system clock interference. In order to obtain the signal in the required frequency band, it is necessary to add a filter to the output end of DDS, and the low-pass filter can better filter the clutter and smooth the signal, so the design of the low-pass filter is particularly important, and the filter characteristics have an important impact on the performance of the output signal.

In order to achieve a better filtering effect, the filter is segmented by a four-choice analog switch and a precision operational amplifier: Butterworth active low-pass filter is adopted, the amplitude of the filter is very flat, and the filter circuit is a second-order Butterworth low-pass filter circuit. The selection of filter frequency band parameters is realized by nINH, S0, S1 control signal output by FPGA to control the gating of analog switch.

UFC718AE101 ABB 使用通道通过UBS连接器传输数据

| ABB DCS | ABB CI626A 3BSE005023R1 PLC接口模块 DRIVES 61061240 | ABB Procontic 07KT94E | 寄存器 |

| ABB DCS | ABB CI626V1 3BSE012868R1、CI626 3BSE004006R1通信接口模块 | ABB ICDG32L1B /GJR5251400R0101 | 电源连接板 |

| ABB DCS | ABB CI627A 3BSC980006R213 CI627-A处理器模块 CI627 库存 | ABB GJR5251800R0101 07TC90 | 整流桥显示模块 |

| ABB DCS | ABB CI630 3BSE011000R1 CI630K02 3BSE011002R1 通讯接口模块 | ABB GJR5251800R0101 07TC90 | 脉冲触发板 |

| ABB DCS | ABB CI631 3BSE016347R1 总线耦合器 AF100接口 双绞线 库存 | ABB GJR5211911P2 | 斩波控制板 |

| ABB DCS | ABB CI810B 3BSE0208520R1 通讯模块 CI810V1 PLC 库存 | Abb 07KT97D | 电气标准器 |

| ABB DCS | ABB CI855K01 3BSE018106R1 MB300接口模块 CI855 库存 | Abb 07KT92C GJR5250500R0202 | 脉冲放大器板 |

| ABB DCS | ABB CI861K01 3BSE058590R1 PLC通讯接口模块 CI861 库存 | ABB GJR2332200R0100 88FT01D | 基础模块 |

| ABB DCS | ABB CI871K01 3BSE056767R1通讯模块 CI871 CI871AK01 | Abb GJR5251300R1101 07KT93C | 摩尔系列模块 |

| ABB DCS | ABB CI920AS CI920B CI920S CI920N S900通讯接口模块CIPB 库存 | ABB GJR5215900R38114 ZE82 | DCS电源模块 |

QQ在线客服

QQ在线客服